關于分層設計的思想,在之前的一篇文章中《嵌入式硬件通信接口協議-SPI(二)分層架構設計模擬接口》介紹SPI接口設計時,已經做了詳細的設計過程講解,在此就不贅述了。

現在參考SPI的BSP層設計思路,用同樣的方法來設計IIC接口的BSP層代碼模塊。

本文將要講解和實現的內容主要分為兩個部分:代碼實現IIC接口管理、代碼實現IIC時序。

IIC接口管理

接口管理的目的是想在后期擴展時,一個工程里可使用多個IIC接口。

這里暫不考慮使用復雜的數據結構,僅僅采用簡單的宏定義,放在頭文件中,省去麻煩的內存申請、分配這一些操作。

以IIC接口序號“1”開始向后排,新增IIC接口時,直接參考當前示例來定義后續的IIC接口序號和管腳即可:

#define IIC_1 1

#define IIC1_PORT_SCL PORTB

#define IIC1_PIN_SCL 6

#define IIC1_PORT_SDA PORTA

#define IIC1_PIN_SDA 2

此處要實現的,依然是位于BSP層的IIC模塊代碼,這個層介于芯片驅動(寄存器)和應用庫之間,要考慮到在后期的移植開發,此IIC模塊可能由IO模擬,也可能由芯片廠商提供的驅動demo實現,所以這里所封裝出來的BSP層接口,一定要考慮到后期的擴展。

所以這里的做法是把參數都放在函數中傳遞,并且均設計成帶有uint8_t類型的函數返回值。這里如此設計的原因和習慣問題,可以參考《【嵌入式編程】函數返回類型設計》一文。

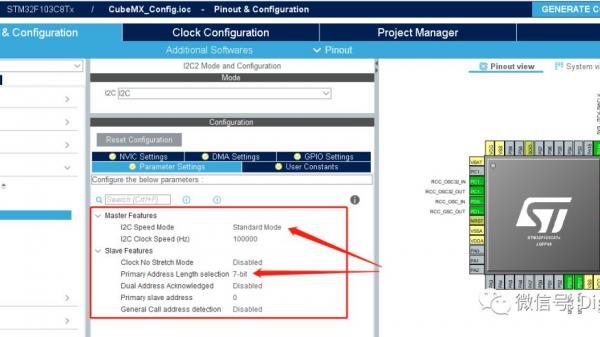

打開STM32CubeMX工具可以看到,在配置IIC接口時,參數可配置內容如下截圖:

參考以上,暫且在結構體中定義:地址位寬、時鐘速率,來定義一個IIC接口對象。如下頭文件中的bsp_iic_obj_t結構體類型。

IIC時序

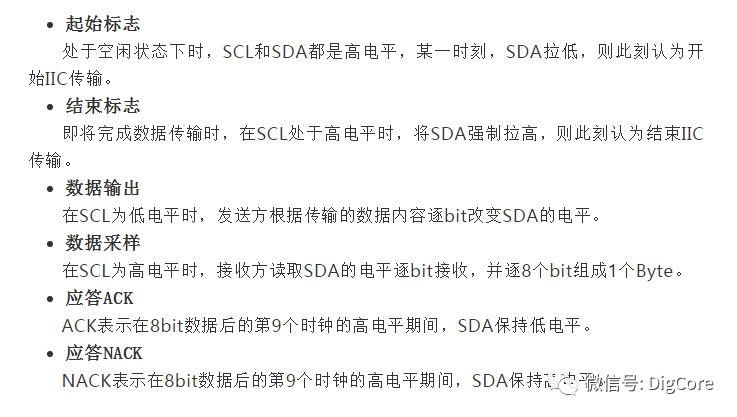

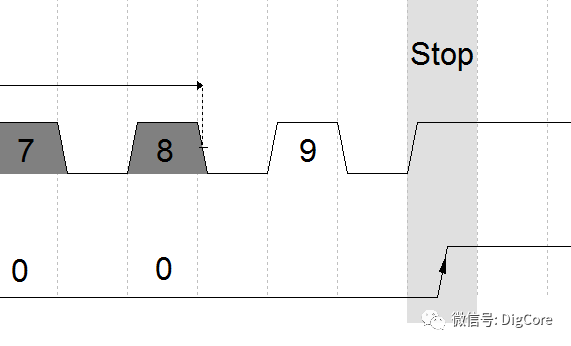

從上一篇《嵌入式硬件通信接口協議-IIC(一)協議基礎》中,我們知道IIC的時序中有這幾種信號特征,現在就根據這幾個信號特征,用代碼逐一實現。

實際上在互聯網上已經有很多關于IIC時序模擬的實現代碼,最簡單的可以從github開源社區、百度百科、各類技術網站,具體到很多的技術論壇都有IIC應用實例,都能找到IIC接口的源碼。

因此IIC時序的模擬已經大同小異了,然而在這里再“造輪子”的目的是,集成、優化、完善自有項目BSP層的代碼,提高項目的擴展性和應用,對屢清代碼的整體框架也有很大幫助!

說白了也是想把這篇文章寫詳細些。廢話少說,立即上碼:

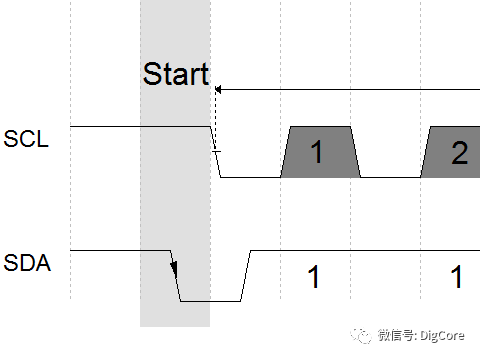

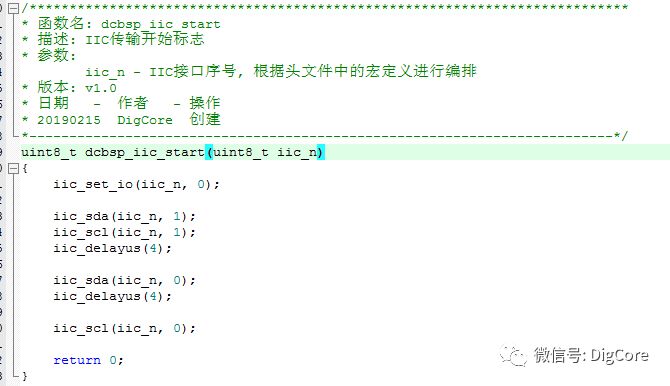

起始標志:

這段起始標志的代碼,思路很簡單,首先確保SDA所使用的IO引腳為輸出,在本BSP層的IIC模塊中使用了iic_set_io(iic_n, 0);函數,將指定IIC接口序號的SDA管腳設為輸出,之后的電平設置,就是完成信號時序的過程。

結束標志

思路類似于上,略。